FET kependekan dari Field Effect Transistor merupakan perangkat elektronika dengan tiga terminal yaitu Source (S), Gate (G) dan Drain (D) dimana arus output FET dikendalikan oleh tegangan input pada terminal Gate, FET dibuat dari bahan semikonduktor tipe P dan N mirip dengan BJT yang membedakan adalah arus output BJT dikendalikan oleh besarnya arus input pada terminal Base sedang output arus FET dikendalikan oleh tegangan pada terminal Gate. FET umumnya disebut juga JFET.

Transistor FET ada dua jenis yaitu :

Junction Field Effect Transistor (JFET)

FET atau JFET pada dasarnya terdiri dari silikon jenis P dan N yang memiliki sambungan atau junction P-N pada dua sisinya. Berikut adalah keterangan tentang channel dan terminal pada FET.

- Gate (G) : Dua sisi semikonduktor tipe N atau P di-doping tinggi untuk membuat junction P-N. Lalu daerah yang didoping disebut dengan Gate (G).

- Source (S) : Merupakan terminal masukan dimana pembawa mayoritas (majority carrier) masuk dan melintas pada semikonduktor.

- Drain (D) : Merupakan terminal tempat keluarnya pembawa mayoritas dari semikonduktor.

- Channel : Merupakan area semikonduktor dimana tempat pembawa mayoritas melintas dari Source ke Drain.

Simbol JFET ditunjukan pada Gambar 1.

|

| Gambar 1. Simbol JFET |

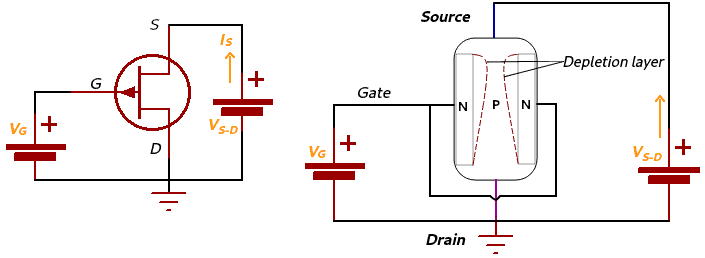

JFET P Channel

JFET channel P adalah JFET yang memiliki lapisan N tipis yang dibentuk pada substrat tipe P dua sisi. Lapisan tipis tipe N pada kedua sisi ini disebut sebagai Gate.

|

| Gambar 2. JFET P channel |

Cara kerja JFET P channel :

Untuk membuat JFET P channel bekerja (meng-on kan) adalah dengan memberikan tegangan 0 Volt pada Gate dan memberikan tegangan positif pada Source (VS) lalu Drain diberi tegangan (VD) 0 Volt atau tegangan lebih rendah dibanding dengan tegangan Source. Saat VG = 0 Volt maka arus dapat melewati dari Source ke Drain secara penuh karena pada saat Gate diberi tegangan 0 Volt maka depletion layer dalam kondisi tipis sehingga daerah channel menjadi lebar sehingga dapat dilewati arus listrik.

Saat tegangan Gate dinaikan maka depletion layer pada kedua sisi Gate akan melebar ke sebelah dalam channel P sehingga jalur pada channel P semakin menyempit yang menyebabkan arus yang melewati Source - Drain akan menjadi kecil.

Bias pada JFET P channel ditunjukan pada Gambar 3.

|

| Gambar 3. Bias pada JFET P channel |

Untuk meng-off-kan atau mematikan JFET P channel ada dua cara yaitu :

- Dengan memutus tegangan bias positif pada terminal Source, dengan demikian tidak akan ada arus listrik yang masuk ke termimal Source.

- Dengan menaikan tegangan bias positif pada terminal Gate hingga depletion layer menutupi daerah P channel. Jika bias positif pada terminal Gate dinaikan sedikit saja maka daerah depletion layer melebar ke arah P channel sehingga daerah P channel akan menyempit menyebabkan arus yang melawati Source menuju Drain semakin kecil. Jika tegangan bias positif diperbesar lagi hingga daerah depletion layer kedua sisi Gate menutupi daerah P channel maka arus tidak dapat melewati Source ke Drain dan dalam kondisi ini JFET dalam keadaan off.

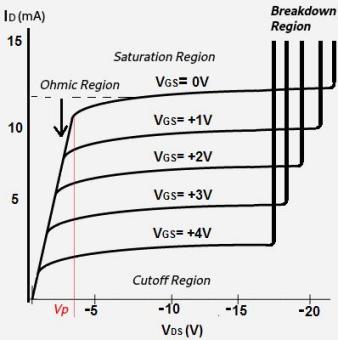

|

| Gambar 4. Kurva karakteristik JFET P channel |

Dari kurva Gambar 4 di atas dapat dilihat bahwa saat tegangan VGS diberi tegangan 0 Volt dan tegangan VSD dinaikan maka arus Drain-Source juga naik, saat VDS mencapai tegangan pinch-off (VP) maka arus yang mengalir pada Drain-Source mencapai titik maksimum atau saturasi (IDSS) dimana jika tegangan VDS dinaikan lagi di atas tegangan pinch-off maka arus tetap akan konstan. Jika tegangan VDS terus dinaikan maka JFET akan mengalami breakdown.

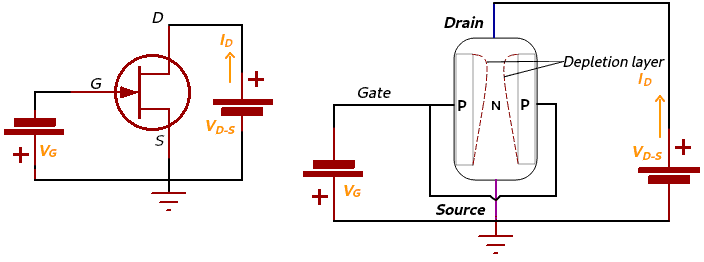

JFET N Channel

JFET N Channel memiliki lapisan tipis semikonduktor tipe P yang dibentuk di atas substrat tipe N. Lapisan tipis tersebut sering disebut sebagai terminal Gate.

|

| Gambar 5. JFET N Channel |

Cara kerja JFET N channel :

Untuk mengaktifkan JFET N channel perlu memberikan bias positif pada terminal Drain dan memberikan tegangan 0 Volt pada terminal Gate (VG = 0 Volt)

Saat Gate diberi tegangan 0 Volt maka depletion layer pada sambungan P-N pada pada kedua sisi tidak mengembang atau tipis sehingga arus dapat melintas dari Drain ke Source dengan mudah sehingga dapat mengalirkan arus.

Saat terminal Gate diberi tegangan negatif, maka depletion layer melebar ke arah dalam P channel. Semakin besar tegangan negatif pada terminal Gate maka depletion layer semakin lebar hingga maksimum dimana akan menutupi atau menghalangi jalur arus dari Drain ke Source sehingga tidak akan ada arus yang mengalir pada Drain atau JFET bisa dikatakan pada kondisi off.

Pemberian bias pada JFET N channel ditunjukan pada Gambar 6.

|

| Gambar 6. Bias pada JFET N Channel |

Untuk meng-off kan atau mematikan JFET N channel ada dua cara yaitu :

- Memutus tegangan bias pada terminal Drain sehingga tidak ada arus yang mengalir ke terminal Drain.

- Memberikan bias negatif pada terminal Gate hingga kedua sisi Gate depletion layer melebar dan menutupi jalur arus dari Drain ke Source. Jika bias negatif pada terminal Gate tidak cukup besar maka depletion layer tidak menutupi penuh jalur N channel sehingga daerah channel hanya menjadi lebih sempit sehingga arus yang melintas dari Drain ke Source menjadi kecil.

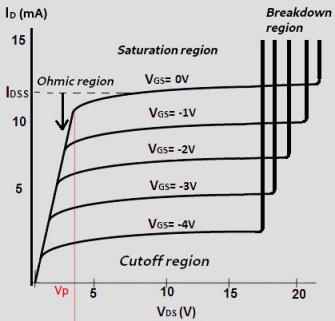

Karakteristik kurva JFET N channel arus Drain (ID) vs tegangan Gate-Source (VGS) ditunjukan pada Gambar 7 mewakili transkonduktansi, atau gain dari JFET.

|

| Gambar 7. Kurva karakteristik JFET N channel |

Dari kurva Gambar 7 di atas dapat dilihat bahwa saat tegangan VGS diberi tegangan 0 Volt dan tegangan VDS dinaikan maka arus Drain-Source juga naik, saat VDS mencapai tegangan pinch-off (VP) maka arus yang mengalir pada Drain-Source mencapai titik maksimum atau saturasi (IDSS) dimana jika tegangan VDS dinaikan lagi diatas tegangan pinch-off maka arus akan konstan. Jika tegangan VDS terus dinaikan maka JFET akan mengalami breakdown.

Pengertian dari tegangan pinch-off (VP) yang telah di jelaskan di atas adalah saat tegangan VDS minimum dimana arus pada Drain (ID) mulai konstan meskipun tegangan VDS dinaikan dengan kondisi VGS = 0 Volt. Dalam hal ini JFET dalam keadaan saturasi.

Penjelasan berbagai region pada kurva Gambar 4 dan 7 di atas :

- Ohmic Region : Area saat JFET mulai menunjukan adanya resistansi terhadap arus yang mengalir dari Drain ke Source (ID). Hanya pada daerah inilah respon kurva yang linier.

- Cutoff region : Area dimana JFET dalam kondisi atau mulai off (tidak ada arus ID mengalir).

- Saturation region : Area dimana JFET bekerja penuh dengan arus ID maksimum. Area ini terjadi saat tegangan VDS berada pada tegangan pinch off dan VGS = 0 Volt.

- Breakdown region : Area dimana JFET mendapatkan tegangan bias pada terminal Drain-Source (VDS) maksimum atau melebihi dari tegangan yang dibutuhkan transistor, lalu JFET kehilangan kemampuan untuk menahan arus karena tegangan yang diterapkan pada Drain-Source terlalu besar. Pada kondisi ini JFET dapat mengalami kerusakan.

RDS = Vp / IDSS

RDS : Ohmic resistance

Jika datasheet JFET menunjukan Vp = 4V dan IDSS=10mA maka besarnya Ohmic region adalah :

RDS = 4 Volt / 10mA = 400 Ohm

Dari dua tipe JFET di atas dapat disimpulan bahwa masing-masing JFET adalah normally on dimana saat terminal Gate bernilai 0 Volt atau tidak ada tegangan input maka JFET sudah bekerja atau on.

Parameter penting pada JFET

1. Transkonduktansi

Merupakan rasio perubahan arus pada Drain (ID) terhadap perubahan tegangan VGS pada kondisi tegangan Drain-Source (VDS) tetap atau konstan.

Besarnya ID dapat dicari dengan persamaan :

ID : Arus Drain.

IDSS : Arus Drain maksimum. Besarnya IDSS dapat dilihat pada datasheet.

VGS : Tegangan Gate - Source.

VGS-Off : Besarnya tegangan Gate - Source yang menyebabkan arus pada ID tidak mengalir.

Dengan VDS = konstan maka transkonduktansi (gm) dapat dicari dengan persamaan :

Untuk menyetel FET agar bekerja pada tengah-tengah daerah operasi maka diperlukan konfigurasi :

- ID dibuat setengah IDSS (ID = 0,5 IDSS)

- VGS = VGS-Off / 4

Saat VGS = 0 Volt transkonduktansi gm disebut sebagai gm0 sehingga VGS-Off dapat dicari dengan persamaan :

Lengkung transkonduktansi dapat dilihat pada Gambar 8.

|

| Gambar 8. Lengkung transkonduktansi |

Contoh perhitungan FET :

Diketahui sebuah JFET mempunyai IDSS= 10 mA, dan gm = 4000µS (didapatkan dari pengukuran).

a. Berapa nilai tegangan VGS-Off ?

b. Berapa bilai VGS agar JFET bekerja ditengah daerah operasinya?

c. Cari transkonduktansi gm pada daerah tengah titik kerja?

Jawab :

a. Besarnya VGS-Off adalah :

VGS-off = - 2. IDSS / gm0

VGS-off = -2. 0,01 / 0,004 S

VGS-off = -5 Volt

b. Nilai tegangan VGS agar bekerja pada daerah tengah (VGS center) :

VGS center = VGS-Off / 4

VGS center = - 1,25 Volt

c. Transkonduktansi pada saat VGS center :

gm = gm0 [1- (VGS / VGS-Off)]

gm = 0,004 [1- (-1,25 / -5)]

gm = 3000 µS

EoF